Have you ever been deep in thought writing and transcribed the words you hear instead of what you intended to write? It was only late in my life that I realized how overloaded my brain becomes when trying to work silently and process spoken words simultaneously. Even if you haven’t experienced the exact phenomenon, the feeling of trying to have a directed conversation among a group of people delivers the same difficulty in trying to address and receive messages in a crowded discussion.

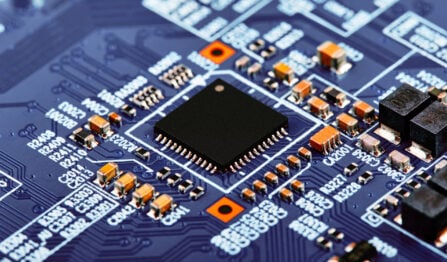

Similarly, signals are not immune to their surrounding environment. The concept of induction is the most common example for those with an electronics background. In induction, a current in one line creates an induced current in an adjacent parallel line via the magnetic field, as Ampère’s Law describes. The strength of this coupling depends on many factors, but its presence can significantly degrade performance during runtime, and detection may be taxing. PCB crosstalk, the generalized term for noise resulting from undesired coupling, is a significant optimization point in mixed-signal or high-speed designs.

How PCB Crosstalk Manifests in Design and Manufacturing

Crosstalk is the unintended influence of a signal by or on another signal. The complex interplay of electric and magnetic fields results in the ability to influence conductor lines without contacting them physically. Crosstalk can occur across two different modes. Those modes include contact and non-contact. Reducing the impact of crosstalk requires first diagnosing its cause:

- Direct – Also known as “conductive crosstalk,” two conductors touching each other can pass the full range of frequencies between them, including the DC bias (also known as the zero-frequency response). Any DC signal then passes through unmitigated, and the resulting signal experiences some offset error at the circuit input or output.

- Indirect – Signals also couple solely through electric or magnetic fields, resulting in capacitive or inductive coupling. Capacitive coupling, alternatively known as AC coupling, removes the DC bias from the signal to prevent issues related to voltage mismatches. Meanwhile, inductive coupling is at the heart of transformers and various other electromechanical devices. However, it can contribute negatively to performance when its presence is inadvertent.

DFM Processes to Prevent Coupling

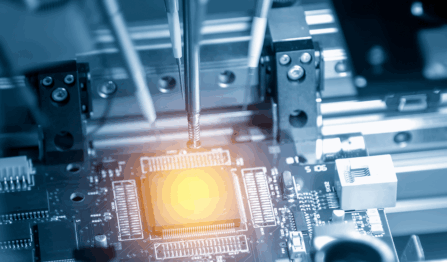

Anywhere conductors intersect unintentionally requires corrective action at the design or manufacturing level. For example, poor solder application/removal and post-production processes like electromigration leading to dendrite growth and spontaneous whiskering could create shorts. As these defects are secondary processes, design can only anticipate the conditions that give rise to conductive crosstalk and attempt to minimize their impact through a battery of aging and environmental tests that guide future revisions (if necessary).

Conductive coupling is unlikely to occur during the manufacturing process thanks to rule checks during design, but capacitive and inductive coupling can be more nefarious. As field strength rapidly decreases with distance, the best approach to resolving indirect coupling is moving traces apart, whether within the plane or across different planes. Further isolation is achievable by flooding the ground on the signal layer to improve a signal’s coupling to it.

General Crosstalk Considerations and Solutions

Distancing traces is an excellent practice but can become challenging to implement in HDI designs due to space constraints. Instead, designers can combat crosstalk with a checklist of some typical troublesome sections of a layout:

- Mixed-signal design – A cornerstone of mixed-signal design is isolating the analog from the digital signals and partitioning the ground plane to prevent background noise due to the high-frequency digital signals. However, designers can take it a step further. Group analog signals roughly by their frequency can prevent aggressor lines from coupling to victim lines of a lower frequency. CMOS components are valued for power efficiency and have high edge rates, which can also impact surrounding signals. Provide adequate spacing around CMOS parts, especially analog signals.

- Timing issues – Clock lines, even digital, are also candidates for noise susceptibility; detection occurs when there are deviations from the true periodicity of the signals (also known as jitter). Ensure that drivers utilize a uniform clock frequency. Multiple clocks in a single package will significantly reduce the signal-to-noise ratio (SNR).

- Embedded signal layers – For a four-layer stackup, the most common arrangement is signal traces on top and bottom, ground on two, and power on three. However, high-frequency designs may want to take advantage of an inversion: signals on the inner layers with planes on the outer layers for additional shielding. This step reduces crosstalk’s overall chance and intensity (provided good layout practices are employed), but some drawbacks exist. The board becomes far more challenging to prototype due to the accessibility and visibility of the signal traces, and while it reduces coupling, troubleshooting occurrences increase in difficulty.

Finally, the cable assembly itself can also create crosstalk. Especially where multiple high-frequency signals are bundled together in the same cable (say in the USB-C protocol), engineering teams need methods to quantify the amount of crosstalk developed by high-speed lines on their neighbors.

PCB Crosstalk Terminology |

||

|---|---|---|

| Capacitive | Two nearby traces experience a parasitic capacitance, with the inside edges acting as parallel plates. The amplitude of the coupled pulse depends on the mutual capacitance value between the two lines. | |

| Inductive | Loop inductance formed between the signal transmission and its return path (usually on an adjacent plane layer) can influence nearby traces depending on the strength of the magnetic field. | |

| Forward |

This half of the coupled signal moves parallel to the original aggressor signal. It is a sum of opposite-polarity pulses and a function of the aggressor signal rise time. Your Contract Manufacturer Talks the Talk, Walks the Walk |

|

| Reverse |

This half of the coupled signal moves antiparallel to the original aggressor signal. It is the sum of two same-polarity pulses and a function of the mutual-impedance value between the lines. Minimizing the possibility of PCB crosstalk ensures designs are well-protected against detrimental and inconsistent performance arising from a layout that doesn’t properly accommodate best practices. Climbing speeds supported by next-generation cellular broadband networks and shrinking band availability is making a case for enhanced attention to crosstalk during design reviews. |

|

There are multiple methods to quantify crosstalk as it is measured relative to the point of disturbance. Near-end crosstalk (NEXT) and far-end crosstalk (FEXT) provide a value for the cable’s crosstalk rejection proficiency. With cabling becoming more robust as demands for data speeds and throughput grow, proper cable shielding will adopt greater importance.

Your Contract Manufacturer Talks the Talk, Walks the Walk

Minimizing the possibility of PCB crosstalk ensures designs are well-protected against detrimental and inconsistent performance arising from a layout that doesn’t correctly accommodate best practices. Climbing speeds supported by next-generation cellular broadband networks and shrinking band availability make a case for enhanced attention to crosstalk during design reviews.

For a manufacturer, detecting these issues is only half the solution. Improving boards and cable assemblies requires an engineering touch. At VSE, we’re a team of engineers dedicated to building electronics for our customers in various life-saving and life-changing industries. With our exceptional manufacturing partners, we instill quality and reliability at every step of production.