When packing a bag for a backcountry trip, I juggle numerous essentials necessary to survive, prepare, and avoid overload. It’s impossible to balance a “perfect” solution – overpack and I’m miserable, pack too restrictive, and I’m flirting with life-or-death situations. It turns out that the best method comes from making reasonable trade-offs, such as researching the weather to determine how necessary rain or low-temperature gear might be.

PCB layout steps follow a similar trend; you can’t perfect all of the design constraints all of the time and it’s simply unreasonable to expect every board to excel in every facet of design. However, a careful layout will make the most of design and space concerns and deliver the best possible performance.

An Overview of PCB Layout Steps

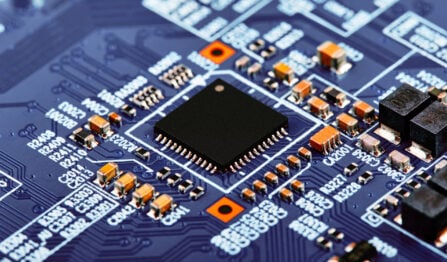

PCB layout typically follows two major design steps: placement and routing. Both stages will require a general heuristic of best practices (which may change depending on the overall function of the board) and input from the manufacturer’s datasheet for any specific inst

ructions. Beginning with placement, designers will want to roughly group the components using the circuits provided in the schematic as a guideline. Balance placing components close enough that traces running between them are short and direct while allowing for fan out to ground and power planes.

Different overall board functions will dictate the best course of action in design, but a generally safe place to start is with any power circuitry. Poorly laid out power circuitry can result in voltages that fail to meet threshold levels in digital circuitry, leading to runtime errors and other difficult-to-diagnose issues.

The Role of the Bypass Capacitor in Power Delivery

Bypass capacitors are a critical aspect of a robust and responsive power network. In effect, bypass capacitors act like localized energy storage devices for adjacent components and networks, providing an alternative source in the event of dips in the performance of the board’s power nets. Placement of bypass capacitors is crucial.

Designers with any level of experience may notice that capacitors will generally be one of two to three different repeating farad values. Capacitors should be arranged around components with the smallest capacitance closest to the respective power pins, ideally routed directly to the power and ground pins. Successively larger capacitors need not be placed as close due to the time constant. The time constant of a capacitor closely resembles that of an RC circuit (there is also parasitic inductance present in the real world, but this can be ignored for a simple estimation). Mathematically, this relationship is defined as:

τ = RC

where τ is the time constant and R and C are the resistance and capacitance, respectively. The relevance of the time constant is it correlates to the time to charge and discharge a capacitor. Therefore, the smallest capacitance bypass capacitors are placed closest to the device’s power pins to provide the quickest response to changes in power net voltage. Larger capacitors do not possess the agility in response as do smaller capacitors but offer additional benefits beyond greater charge storage, specifically in the realm of frequency response.

How Stackup Design Promotes Signal and Power Integrity

The stackup design will have major implications on the overall performance of the board. Having well-placed ground and power planes will ensure excellent power delivery and return paths. First, the order of the stackup needs to be decided upon. The actual distribution of signal and plane layers will differ tremendously depending on the board’s characteristics, but a safe assumption is that the top and bottom layers will function as routing layers; for a small layer count board, the top and bottom may be the only routing layers. Ground and power layers are often paired up within the stackup.

Most importantly, the board should have some internal symmetry across the core between the plane and signal layers. As an example, a six-layer board might look like signal layers on top and bottom and layers 3 and 4 with ground and power on 2 and 5. This provides a solid reference plane in between routing layers, ensuring a short and direct return path to reduce EMI emissions. A rule of thumb for stackup planning: each new pair of signal or plane layers will be inserted into the innermost layers and will alternate function with the previous layer pair (i.e., signal to plane or plane to signal).

Tips for Better Performance and Board Management

The power plane or planes provide the coverage and surface area necessary for the thermal and electrical needs of the board’s power nets. Not only do copper features need to encompass the net, but the design must avoid excessive tapering that can result in hot spots and choke current delivery. In most designs, each power net can’t occupy a single layer – copper shapes must be formed that capture all or some of the vias of a specific power net and no others. While the layout should be flexible enough to accommodate some rearranging, shrewd designers can maximize their power plane coverage by expanding in the z-axis rather than in the plane. These polygon features must overlap at locations with multiple via connections to accommodate the current running over a greatly reduced area.

Adjacent signal layers pose a problem of coupling when routed parallel – capacitive coupling over long enough distances (essentially a pair of differential signals in the z-axis) can greatly affect the integrity of both. Beyond the stackup, designers can sidestep capacitive coupling in adjacent signal layers by alternating between a vertical and horizontal routing schema. This method ensures that signals have only a momentary space of overlap for which coupling can occur, ultimately driving down its effect.

Your Contract Manufacturer Will Draw Out the Best Performance

You don’t just want your board to function – you want it to exceed all expectations. The best performers will yield the best performance: at VSE, our work is dedicated to building electronics for customers by our team of engineers. Along with our partners, we will make sure no detail goes unexamined — from PCB layout steps to quality control — when it comes to optimizing your board.