Despite the best efforts of engineers, designers, and manufacturers, PCBs cannot function in a textbook-ideal manner. The real world is full of irregularities that are impossible to eliminate; instead, it’s the job of these teams to mitigate nonidealities to the point of negligibility. One of the biggest challenges – especially with increasing digital rise/fall times – is to account for noise in the design. PCB noise can cause extreme reliability issues, and the ability to couple with surrounding electronics can produce extreme system instability.

| PCB Noise Best Practices | ||

|---|---|---|

| Preferred | Not Recommended | |

| Stackup | Signal layers adjacent to a ground plane | Signal layers nonadjacent to a reference plane |

| Crossing Split Planes | Never – results in circuitous return paths with high EMI | As needed |

| Decoupling Capacitors | Use of many decoupling capacitors for a range of frequency responses | Using a single decoupling capacitor value |

| Ground Planes | Organizing/isolating digital and analog ground | Single ground net |

| Board Perimeter | Guard fence around the edge of the board and plane/signal keep-out area | No fence and planes/signals extending to board edge clearance |

| I/O Isolation | Organize all off-board connections toward the board edge to minimize interaction with local circuits | Layout I/O without regard for nearby signals |

The Different Domains of PCB Noise

Noise is a byproduct of electromagnetic waves generated during regular circuit operation. At some level, noise is unavoidable – while mitigation techniques are necessary to limit its impact, designers can’t expect to eliminate it. Critically, there is no magic bullet for EMI reduction in a PCB: designers must carefully examine all layout aspects to ensure acceptable EMI emission levels.

Stackup

Current only flows in a closed loop, but it can be challenging for designers to understand the return loop for a signal when routing hundreds or thousands of discrete signals. As the size of the loop increases, more magnetic field lines (and thus, more magnetic flux) flow within the current loop, making it more susceptible to magnetic coupling with its surroundings. The simplest way to shrink the size of the loop is to ensure the return signal has an adjacent ground plane instead of traversing one or more planes to begin its return path. Ideally, every signal plane should be adjacent to a ground plane. If this stackup configuration is incompatible with the design, an adjacent reference plane may suffice but can also contribute to EMI issues.

Split Planes

When designing reference planes (especially for power nets), dividing the plane into multiple smaller copper regions assigned to distinct power nets is common. Designers must avoid routing over the splits in these planes for signals referencing these layers; routing over split planes lengthens the signal’s return path and creates a much larger current loop (i.e., greater EMI concerns).

Decoupling Capacitors

For signal integrity, decoupling capacitors provide a low-impedance return path to ground that keeps the high-speed noise generated from digital components away from susceptible circuitry. However, an individual decoupling capacitor’s frequency response is unlikely to cover the noise’s frequency range. Combining the effects of multiple decoupling capacitor values provides a more comprehensive noise solution.

Ground Planes

While ground is ground, mixed-signal boards must contend with digital components producing noise that can easily overwhelm analog signals. By physically isolating the analog and digital components, designers can assign “separate” ground nets to the digital and analog circuits. Note that these grounds are technically indistinct and tied together at a single point between the ADCs/DACs, which have a high input impedance to block noise between the grounds. Connecting the grounds this way minimizes the ability of noise to propagate through other low-impedance pathways.

Board Perimeter

Designers can effectively contain electromagnetic energy by creating a physical barrier at the board’s edges. First, designers should enforce a keep-out area at the board edge to block high-speed signals or transients from coupling with nearby conductors. Second, a grounded via fence can limit the coupling ability at the conductive edge of the board by providing a low-impedance pathway for outgoing and incoming EM waves. Ensure the via fence is split at some point, as a large ground loop can act as an antenna and intensify EMI issues.

I/O Isolation

Like the analog-digital circuit split, designers should place and route off-board connections away from circuitry that is exclusively local to the board. This arrangement minimizes the potential for noise generated by the off-board system to couple to the board (and vice versa). Ground pours on the outer layers help further isolate off-speed signals in the case of distinct high/low-speed off-board connections.

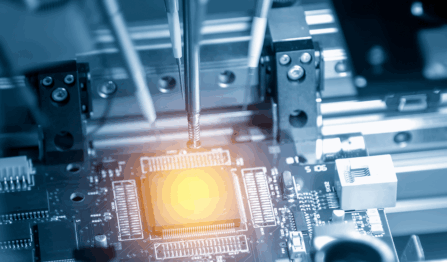

Your Contract Manufacturer Cuts Through the Noise

PCB noise best practices require diligence at every level of the design process, starting with the stackup. The challenge with noise is that it is purely a product of the design stage (except for certain circuit elements like decoupling capacitors and terminating resistors), meaning the designer is responsible for passing EMI testing. Preparing a design to pass EMC can be challenging, but VSE is here to help. Our engineers are committed to building electronics for our customers, including a full design review before entering production. We’ve been realizing life-changing and life-saving devices for over forty years with our valued manufacturing partners.