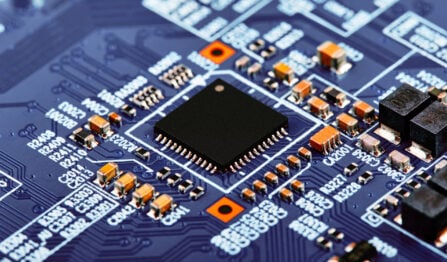

Modern expectations for many electronic devices are akin to a Swiss army knife: every reasonable feature that users may want should be available. Intuitively, this makes sense: if component costs are reasonable, it’s much easier to include additional features that may see less general use than to revise a design to include them after manufacturing. The knock-on effect of this approach is denser designs where board area comes at a premium, especially in portable devices or those with strict form factors. Accommodating these multiple constraints requires a more intricate fabrication: enter sequential lamination. Sequential lamination is a multi-step (2 or more) lamination process that allows manufacturers to shrink interlayer connections for more precise placement and overall board space optimization.

Modern expectations for many electronic devices are akin to a Swiss army knife: every reasonable feature that users may want should be available. Intuitively, this makes sense: if component costs are reasonable, it’s much easier to include additional features that may see less general use than to revise a design to include them after manufacturing. The knock-on effect of this approach is denser designs where board area comes at a premium, especially in portable devices or those with strict form factors. Accommodating these multiple constraints requires a more intricate fabrication: enter sequential lamination. Sequential lamination is a multi-step (2 or more) lamination process that allows manufacturers to shrink interlayer connections for more precise placement and overall board space optimization.

| Sequential Lamination Tips | ||

|---|---|---|

| Outer Layers | Inner Layers | |

| Materials | Z-axis CTE ≤ inner layer substrate Z-axis CTE | Low Z-axis CTE, high Tg |

| Stackup | Higher resin content to spread stress over a larger area | Lowest reliable resin content |

| Layout | Avoid copper pours over buried vias | Keep copper area coverage high to improve resin over copper and limit copper thickness concentration after plating |

The Motivation for Sequential Lamination

Sequential lamination is a subsequent laminate-and-drill stage of PCB fabrication beyond the traditional single step. It can be a significant cost adder due to additional processing and reduced yield; however, it remains a popular method because it can solve complex, high-density interconnect (HDI) layouts with minimal layer assignment. This approach reduces board thickness, which can be especially valuable for tight form factors or mechanical advantages (reduced weight, less flexure, etc.)

Broadly, HDI comes in two categories:

- Standard HDI uses a 2-4 layer core and 1-3 sequential layers on both sides of the core (i.e., a 4-10 layer stackup when finalized). The core uses through-hole drilling, while the outer layers on either side of the core use microvias.

- High-layer HDI is similar to the standard mode but with a much thicker core (6-26 layer counts are ordinary) that employs stacked and staggered microvias. Additional outer layers attach identically to the standard method above.

Sequential lamination allows fabricators to introduce microvia structures into the stackup. Unlike traditional through-hole vias, microvias only span some of the vertical layers of the board by design. This setup has two primary advantages: microvias can reduce hole diameter/annular ring beyond what is possible with a typical through-hole, and the board area usually occupied by the through-hole on layers unspanned by the microvia is free for routing or placement. The former is known as the via aspect ratio and acts as a lower limit on hole diameter/annular ring; a maximum aspect ratio of 10:1 (that is, via depth to via diameter) can inhibit consistent plating along the length of the via barrel that can cause intermittent connectivity issues or complete mechanical failure of the plating. While the microvia has a maximum aspect ratio of 1:1, its depth (and therefore hole diameter) is less than 0.25mm/10 mils, allowing for significant reductions in hole area.

Fabricators categorize microvia structures with two descriptors: whether they are visible on an outer layer after the final lamination step and their orientation to other microvias that combine to form indirect through-hole continuity. Blind microvias are present on one external layer, while buried microvias span two internal layers. Stacked microvias share the same x-and-y-position across layers (i.e., they stack on each other when moving up or down the stackup). In contrast, staggered microvias use traces to connect between microvias on the same layer for different in-plane x-and-y-positions.

Material Considerations to Improve Fabrication Outcomes

Introducing microvias to a stackup carries a greater risk profile due to internal stressing related to the coefficient of thermal expansion (CTE) mismatch between copper and most substrate materials in the z-axis. As heat expansion causes varying (and sometimes considerable) strain between the microvia pad and surrounding substrate, defects can range from open circuits as the pad lifts off the barrel to catastrophic failure by delamination. Standard FR4 materials that are well-suited for designs without sequential lamination may encounter a higher incidence of failure during repeat laminations.

Therefore, selecting appropriate substrate materials is paramount to improving yield and maintaining a cost-competitive design: a low-Z-axis CTE substrate (typically 50 ppm/℃ or less) is a much closer match to the z-axis CTE of copper and reduces pad lift and delamination. The glass transition temperature (Tg) also plays a role, as higher Tg values keep the substrate material hard and structured instead of rubbery and viscous during the high lamination heat. Finally, reducing resin content helps control z-axis expansion as the glass fibers have a much lower z-axis CTE than the epoxy.

Your Contract Manufacturer Handles HDI Designs and More

Sequential lamination has increasingly become required for high-density circuits with miniaturization of devices and numerous circuit functions/features. However, it significantly increases per-board costs during fabrication, and poor DFM methodology can drastically reduce the reliability of microvias. Fortunately, designers can rely on VSE, whose team of engineers is committed to building electronics for their customers. We collaborate closely with designers to revise, optimize, or introduce new devices that exhibit quality and reliability to the market. We’ve been realizing life-changing and life-saving devices alongside our valued manufacturing partners for over forty years.