Nearly everyone has experienced a pressure cooker-type class in engineering. These courses typically take a “tough love” approach to student success to drive core concepts home, culminating with extensive tests that can make-or-break grades. Suffice it to say most students do not eagerly anticipate these classes, yet they often form the backbone of a curriculum due to their resemblance to a demanding workplace environment.

Testing aims to ensure an aspect under evaluation will perform satisfactorily. Printed circuit boards used in the telecom industry must pass vital testing to ensure they will function as expected in their intended operational environments. Highly Accelerated Life Testing (HALT) is one of the primary methods for establishing the breaking point of devices before further refinement. A PCB contract manufacturer (CM) invests significant effort into cre

Types of Failure Modes |

||

|---|---|---|

| Description | Mitigation techniques | |

| Overstressing | Applying stress conditions that exceed the material’s threshold strength for a particular parameter. | Running a device according to manufacturers’ ratings should prevent overstress events. Incorporate redundant and protective elements that extend maximum durability. |

| Wear-out | A lifetime accumulation of stressors ultimately leads to failure in the device. | Wear-out is inescapable, but careful management of operating conditions will optimize device service life. |

| Performance | As components age, drift in mechanical, electrical, and material attributes occur; performance and, eventually, overall function degrade and may no longer possess the necessary characteristics to meet the design intent at production. | A subset of wear-out, performance drift is a natural result of material aging. If reasonable, repair or replacement of components may be an option, but in-system verification can be daunting. |

| Variance | No matter how tightly controlled the manufacturing is, no two components, devices, or systems can be identical due to unavoidable fluctuations in materials and processes. | Tolerance in DFM encompasses this lack of repeatability. |

Highly Accelerated Life Testing is a Cornerstone of Stress-Testing

Electronic equipment can be subject to harsh environments to determine susceptibility to real-world conditions. It is not feasible to test a device for its entire service life, which may extend years; product development would outlast the technology powering the design. Instead, automating the process of device interaction and compacting aging conditions provides manufacturers with a framework that satisfies both customer confidence and market demand. To thoroughly test this equipment, it’s necessary to mimic the operating environments, which may differ according to general device requirements or more specific needs.

There is some nuance between HALT and Accelerated Stress Testing (AST), although HALT is a component of AST. While both reveal problems in days instead of years that traditional testing would take, HALT focuses on stimulation testing (that is, “testing to fail”) versus simulation testing, which generates failure expectations; the former test mode implements a structure where the purpose of the test is studying the defect modes to provide an accurate approximation for field use conditions and longevity. There is a vital wrinkle in the “test to fail” format. However, test methods must simulate the product life and not the failure event specifically. Test engineers then use data gathered from HALT and lifecycle modeling to estimate the failure point of devices in real-world settings.

Using HALT for Iterative Revisions

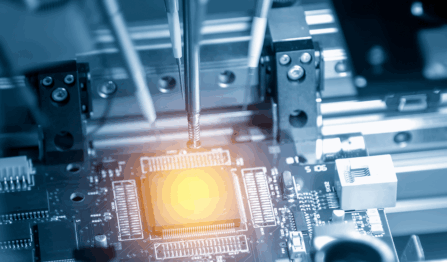

HALT detects problems in product design, component selection, and manufacturing. The product sample under review undergoes stress levels that progressively increase throughout the test, including rapid changes in temperatures and vibration. Testing continues until the product fails to determine how far above its specified stress level operation persists. Once completed, the HALT will provide data on the different stress characteristics of the product, allowing the design and manufacturing processes to adapt as necessary.

As HALT is only a piece of most testing regimens, it has some notable drawbacks in application. The format excels at producing fatigue through failure, but the exact point of failure is impossible to identify. In actuality, HALT models the fatigue of the device rather than its lifetime performance, but this distinction is often inconsequential.

How A CM Builds out HALT

HALT aims to incorporate test data into future revisions to bolster the design’s resilience, improving its environmental suitability and performance applicability. Growing the number of stressable environments reinforces the individual conditions, improving total performance irrespective of field use location. Since stress levels hinge on the product in development (devices shape the test selection, not vice versa), the earlier HALT data folds into designs, the better the outcome. As a destructive test, it sets the operational limits for nondestructive and simulation testing.

The general structure of test-informed revision is a test, analyze, and fix model (or TAF) that takes the gleaned insight from HALT results as the basis for further revisions. A pillar of TAF is the failure of devices in expected ways; devices that do not fail or fail unintentionally require an examination of the test scenario to ascertain applicability. Correct failure during testing is a positive sign in that it shows the device and test are compatible but should be the catalyst for additional bolstering of the design.

While conducting HALT on a circuit board, the PCB CM will start by developing a detailed testing plan with your engineering and reliability teams. This testing plan should include the following:

- Product and testing specifications.

- Testing procedures, instructions, and recording processes.

- Incorporation of testing into the masterwork and process flow.

Once all parties approve this testing plan, it should be released through a document change order to become part of the overall PCB build documentation.

The CM will use an environmental chamber to conduct the tests as it allows for a fine level of test control. This chamber affords control over multiple stress parameters–such as temperature and humidity–while the device under test (DUT) powers up. The chamber has access ports for PCB inputs and outputs and power for the board to be operational while being tested. Depending on the board’s requirements, a CM may also choose to use the services of a third-party tester. This option can allow higher volumes of board throughput, providing more strenuous testing or accommodating larger board sizes.

Your CM Has a Handle on HALT, and Other Test Methods

Highly accelerated life testing is the beginning of the benefits of working with a contract manufacturer on a PCBA. In addition to understanding the testing needed and having the resources to accomplish that testing, a CM with telecom experience will already have the manufacturing and documentation processes installed to save time and eliminate errors.

At VSE, we have spent years providing service to our partners in the telecom industry. We understand your particular manufacturing requirements, and our processes already include the critical inspection points you require. Our copy-exactly process ensures that once the build configuration for your telecom product is locked in, it will remain that way during its production run without any modifications. And when you decide to make modifications, you will benefit from clear and concise communication with us through our documentation and tracking systems.