I try to avoid clutter in small spaces – sometimes even at the expense of good taste. One of my favorite space-savers is the over-the-door shoe rack. It may look a little tacky, but it conserves a large amount of floor space in an area that, for most, goes unused otherwise.

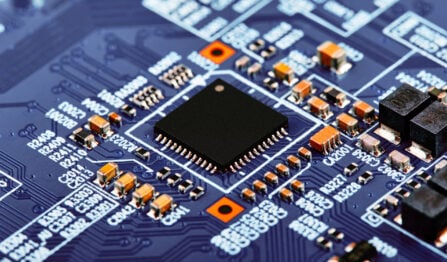

PCB layout design is even more concerned with functional multi-use space. Via-in-pad is the fabricator’s ultimate solution to ever-decreasing component pitches that requires more signal fanout in a smaller area. Since pads are component-defined (with some leeway for the manufacturer), placing vias in pads uses space already reserved for soldering and saves precious routing area. While via-in-pad impacts fabrication cost/yield due to the increased difficulty of maintaining reliability, it can sometimes be the only method to fit a dense assembly within a constrained board area.

ADVANTAGES AND DISADVANTAGES OF VIA-IN-PAD |

|||

| Considerable space savings for HDI designs | Adds additional processes while reducing yield; a substantial cost adder | ||

| Cost addition is less significant if the stackup design is already using microvias | Through-hole incompatible | ||

| Better sub-layer registration | Poor processing can introduce additional defect vectors to fabrication and assembly (outgassing, voids) | ||

| Can improve thermal routing with conductive via fills | |||

The Variations of Via-in-Pad Processes

Via-in-pad is closely associated with microvias. Unlike through-hole vias, microvias generally only span two layers at a time (the IPC rule is that their depth is, at maximum, no greater than the diameter of the hole or .25 mm, whichever is less). The depth restriction leads to two possible configurations:

- Stacked microvias are equivalent to a through-hole. However, the stacked alignment encounters additional fabrication difficulties.

- Staggered microvias are unaligned in the z-axis and can place in any location on a layer pair (a trace will need to connect two microvias if they function as a through-hole connection).

The via size will depend on two factors:

- The aspect ratio, or the ratio of the drilled hole depth over the hole diameter, limits the minimum diameter. For through holes, the drilled depth is the width of the board. An aspect ratio of 8~10:1 is acceptable for through-holes without incurring excessive fabrication defects relating to plating and thermal stress accumulation around the via barrels. Microvia aspect ratios are far smaller, maxing out at 1:1 of the hole depth to diameter.

- The IPC class of the board reflects the inspection criteria for the board’s application. An increase in IPC class indicates tighter tolerances and generally enhanced feature sizes to prevent service interruption. In the case of vias, this equates to larger annular rings – this doesn’t affect the size of the drilled hole but increases the width of the pad around it.

Note that wander during the drilling process will automatically increase the size of mechanically drilled vias – the tolerance accounts for this. Ultimately, an eight mil drill can result in a via pad of up to twenty mils, depending on the IPC classification requirements.

A significant reduction in hole size and pad size is achievable with microvia laser drilling, and modern HDI designs use this fabrication technique for several reasons. First, BGA breakout is unachievable without it: pitches ≤ .5 mm may exceed the lower limit of manufacturability for trace widths and mechanically drilled vias. Laser drilling is also far more accurate for registration purposes than standard drilling, ensuring sub-layer alignment to the artwork’s plane.

Regardless of the drilling mechanism, via-in-pad requires a construction from the barrel of the hole to the surface pad that binds the structure together during standard thermal expansion/contraction cycles. The barrel plating can extend continuously onto the pad’s surface, enclosing the via-in-pad, or a secondary metallization process is available (filled and capped via).

Size and Fill Type Affects Via Applications

- Smaller hole diameters are more likely to achieve complete solder wetting, which impedes the inflow or outflow of process materials. Corrosive liquids may remain trapped during rinsing, and voids may result from etchant attacking electroplated copper where the surface finish was incomplete.

- Solder paste will cover via-in-pads during assembly. During reflow, a gas bubble can migrate into the microvia, forming a void in the solder joint, resulting in poor connectivity.

Voids are permissible during an inspection, but higher IPC classes are more restrictive on the area they may occupy. Filling vias reduces voids’ occurrence and size significantly compared to the conformal plating (no-fill) method. Via filling relies on drilled hole sizes between 8 and 18 mils that are large enough to allow common via-fill material to push through while simultaneously being small enough to prevent its escape.

Via-fill materials can be conductive or non-conductive; this does not affect the electrical characteristics of the via but alters the thermal performance. The vast majority of filled vias feature non-conductive materials as its better suited to the coefficient of thermal expansion (CTE) of most substrate materials. Throughout the board’s service life, a via-fill CTE that closely matches the CTE of the surrounding substrate is less likely to fail thermomechanically from the stresses caused by heating/cooling cycles.

However, thermally conductive via fills play a vital role in the aptly named thermal vias. While all vias are thermally conductive across the copper plating, thermal vias function more explicitly as thermal routing channels away from active components that generate large amounts of heat – think power supply components, BGAs that run hot, or thermal pads under QFPs. In effect, thermal vias provide rudimentary heat-sinking abilities in locations or assemblies where standard heat sink designs would be incompatible.

Your Contract Manufacturer Knows the Ins-and-Outs of Via Design

Via-in-pad is an indispensable board fabrication technique that uses existing board space to double dip on functionality, giving designers extra routability to complete HDI layouts; this comes with a literal and figurative cost to manufacturers. Design teams should carefully weigh their options as to whether via-in-pad is necessary. Assuaging a design may be easier said than done, especially with product teams with less experience in DFM. Fortunately, our engineering team is committed to building electronics for our customers, ensuring a lean manufacturing process with excellent time-to-market. With our valued manufacturing partners, we here at VSE are proud to play a part in creating life-saving and life-changing devices for multiple industries.