Once the family hears you have some background knowledge of electronics, conversations quickly become, “Y’know, I have this device that went on the fritz recently.” Perhaps an evolution of the fledging IT role many computer-savvy teenagers played, those in the industry are aware of how difficult even diagnosing some electronics issues are, much less their repair.

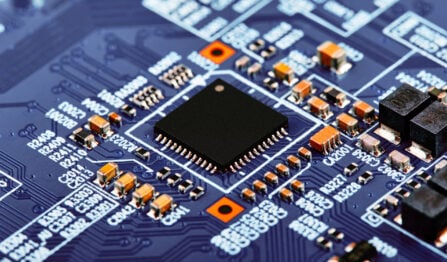

Sure, a solder job is easy enough with an iron and a steady hand, but malfunctions emanating from the board are nearly impossible to correct. As electronic devices have become more sophisticated, the board itself has become a component in many ways that requires a significant amount of engineering design. To counter this mounting complexity, fabricators use a test coupon to enact quality control across the many manufacturing processes.

The Role And Standards of A Test Coupon

Test coupons are manufacturers’ primary mechanism to verify PCB production processes. Unlike electrical testing, which typically only measures the performance or function of board features, test coupons allow observers to evaluate form and design. The difference is subtle but essential: function may be intermittent over device operating conditions (sometimes befuddlingly), and mechanical/material characteristics are always at the core of issues.

The test coupon is a sacrificial piece of a PCB panel explicitly reserved for destructive analysis. Associating the coupon with the panel in this fashion has a higher likelihood of creating a representative testing sample that accurately reflects the manufacturing environment of the boards.

Coupons are valuable as they enable destructive testing without impacting yield, so long as the coupon size doesn’t preclude additional boards through panelization, although this is unlikely. Test coupons have two potential drawbacks:

1. The coupon separates from the board(s) it represents. Poor tracking and organization may result in the unavailability of the coupon when further assessment is necessary.

2. The fabricator designs the coupon features, not the person or team performing the PCB layout. Multiple designers at different stages can introduce an additional source of error when test structures do not adhere to the corresponding layer’s single-ended or differential pair impedance.

While important, effective communication between design, testing, and fabrication facilities can circumvent these errors with proper documentation practices. Additionally, including the test structures within the board can take up significant real estate – impedance test traces can occupy a run distance greater than three inches – making them highly unsuitable for HDI designs or small enclosures.

As destructive testing supports multiple methods of manufacturing analysis, IPC has defined conformance parameters for multiple coupon styles within IPC-2221B. This piece will not dive into the minutiae of the IPC standard but instead provide the reader with an idea of the different analysis modes and their suitability to PCB manufacturing processes.

Coupon Types (as adapted from IPC-2221B)

Coupon |

Test feature(s) |

Purpose |

|

AB/R |

General through-hole features | Evaluates PTH/vias, thermal stress, clearance, registration |

|

A/R |

General through-hole features (no vias) | Evaluates PTH, thermal stress, clearance, registration |

|

B (propagated) |

Vias (blind, buried, through, filled, etc.) |

Evaluates vias, thermal stress clearance, registration |

|

E |

Moisture insulation |

Moisture insulation resistance |

|

S |

Hole solderability |

Evaluates hole solderability |

|

W |

Surface mount solderability |

Evaluates surface mount solderability |

|

D |

Daisy-chain via |

Plating/via thermal stress |

|

D (propagated) |

Daisy-chain propagated via |

Plating/via thermal stress |

|

G |

Solder mask |

Solder mask adhesion |

|

H |

Surface insulation | Surface insulation resistance |

| P | Peel strength |

Peel strength/plating adhesion |

| Z | Controlled impedance |

Controlled impedance |

| K | Registration |

Verifies clearance of internal plating/copper features |

Additional Detail on IPC Test Coupons

AB/R

A combination of the legacy A, B, and R coupon features, AB/R improves on the three by adding a C feature for the via or component hole with the smallest annular ring. B features check the internal lands on the layers closest to the top and bottom, signal layers, and plane layers. This coupon is still compatible without B features, although the fabricator will need to edit the drill file before and after generating the coupon. R features establish registration, but a variance in foils heavier than 1 oz. precludes their usage. Similar to the AB/R, the A/R coupon is applicable for boards without vias.

B (propagated)

B coupons evaluate variant via structures, such as a combination of (un)filled through-holes or blind/buried microvias, that are outside the scope of the B features of the AB/R coupon. The propagated B coupon aligns with the D coupon structures for feature testing and lacks the registration features of the AB/R, but otherwise, its intent is the same as the AB/R. Each B coupon supports two via structure styles, with the vias further subdivided into an upper and lower half. The top half is used for registration purposes, while the bottom examines structural integrity.

E

These coupons check the moisture/insulation resistance of the laminated substrate material at a maximum of ten layers at a time. Boards with greater than ten layers must have additional coupons of up to ten layers that start on the layer of the last coupon.

S

These coupons evaluate through-hole solderability. While representative copper layers may remain on internal layers, coupons must suppress all internal pads.

W

This coupon uses a double-sided pattern for surface mount solderability evaluation. Neither inner layer patterns nor solder mask is included for this coupon, while copper is added to the inner layers to match the PCB thickness.

D/D (propagated)

The D coupon types evaluate via and general hole plating reliability with thermal stress testing. These coupons use via structures in a daisy-chain formation to measure resistance, with the propagated D coupon evaluating more complex via structures as outlined in the propagated B coupon: (filled) through-holes and blind/buried vias (stacked or staggered) are all valid structures, but each coupon can only test for two structure styles.

G

Measures solder mask adhesion over three regions: copper/surface finish, laminate, and interconnect conductor width.

H

H coupons quantify the effects of residues on surface insulation resistance with an interstitial comb pattern on each side.

P

P coupons determine the peel strength of foils laminated to the outer layers with a conductor pair on both sides.

Z

Z coupons verify the impedance value of controlled impedance lines of the board. Each layer allows for two single-ended or differential pair impedance structures, with a total capacity for 24 single-ended lines, 12 differential pairs, or a combination of the two structure types.

K

K coupons check for clearance between copper on internal layers and hole plating; tests for shorts between these features using an ohm meter.

Your Contract Manufacturer Knows PCB Design Inside and Out

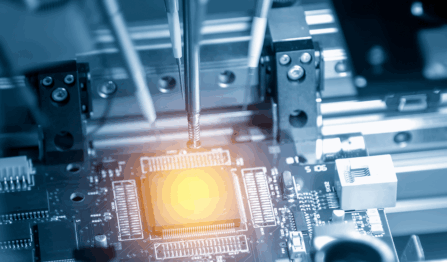

Test coupons offer tremendous insight and feedback on PCB design and manufacturing processes. Instead of having internal features limited to X-ray inspection techniques, fabricators can quickly assess and correct processes, saving themselves and their clients valuable time and money.

End-users also benefit from coupons in the inspection process as it enhances reliability and improves overall performance outcomes of the board. PCB manufacturing is an involved process, but the engineers at VSE are committed to building electronics for our customers for a bevy of life-changing and life-saving applications. Alongside our valued manufacturing partners, we’ve dedicated our professional experience to improving board quality and customer satisfaction over the past 40 years.